(1)

理解摩尔定律未来发展的路线图, 对理解 GPU 计算能力的进步速度, 和人工智能技术的进步速度的重要性.

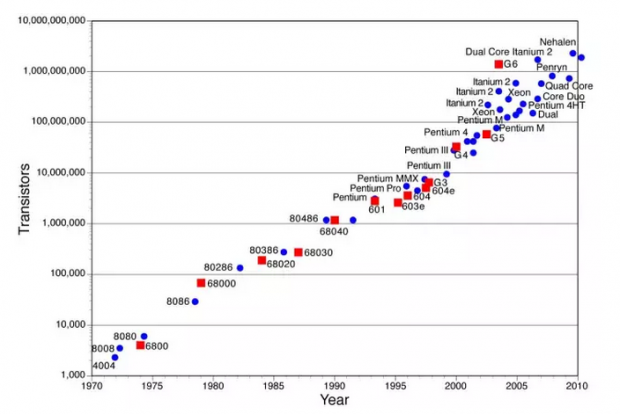

摩尔定律的传统定义是: 半导体芯片上的晶体管密度,平均每 18-24个月翻一番.

它最初于1965年四月被芯片公司英特尔的创始人 戈登*摩尔 (Gordon Moore) 在一篇名叫 "把更多零件塞到集成电路里" (Cramming more components into Integrated Circuit) 的论文中提出.

2013 年八月,曾就职于英特尔任总设计师的 Bob Colwell 在芝加哥的一个行业会议上宣称: 芯片行业的摩尔定律要终结了.

"从计划的时段来看,我认为 2020年可能是摩尔定律最早的终结时间. 你也许可以说服我拖到 2022年, 但不管它 (栅长, 晶体栅极的最小线宽)是到 7 纳米, 或者 5 纳米,这 (摩尔定律的终结) 是一件大事. " ( 普通人的头发直径大约 75000 纳米)

Colwell, 不是第一个, 也不是最后一个,预测摩尔定律即将终结的人.

摩尔本人, 曾在1995年预测, 摩尔定律将于 2005年终结.

2015年, 摩尔本人, 再次预测, 摩尔定律将于 2025年终结.

最近的关于摩尔定律终结的各种预测, 最主要的理由,是到2025年之前,如果栅长缩小到只有 3纳米,其长度只相当于十个原子的大小. 在这个尺度,电子的行为方式将进入量子力学测不准原理的领域,晶体管可靠性将完全无法保证. 另外在这个尺度,晶体管的散热和芯片的生产成本控制,看起来也是无法逾越的技术挑战.

摩尔定律真的会终结吗?

如果会,是不是意味着科技发展将停滞不前,人类一起在地球上混吃等死?

如果不会,它对未来人类文明的进步,又意味着什么?

(2)

在展望未来之前,非常有必要回顾一下摩尔定律过去五十年的演变.

摩尔最初在1965年论文中提出的晶体管密度的概念,不是芯片上最多可以安放多少晶体管,而是从生产成本角度看,晶体管数目的最优值.

生产芯片时,增加晶体管数目一般会降低晶体管的单位成本.但是数目超过一个临界点,芯片生产出现瑕疵的几率增加,开始抵消密度增加的好处.集成电路的设计和生产,最终都是要寻求一个最优点.

摩尔在 1965年的预测, 是十年内,晶体管的密度,每年都会翻番.到1975年,一个芯片上的晶体管数目,将从 1965年的 64个增加到 1975年的65000 个.

后来英特尔在1975年生产的一个内存芯片 (面积为四分之一平方英寸, 折合约 161 平方毫米) 的晶体管数目达到 32000 个, 和摩尔的最初预测非常接近.

1975年摩尔在一篇论文中总结了前十年芯片密度增加的主要原因:

1.晶体管小型化

2.芯片面积增加

3. 新的设计技巧提高空间的利用率.

但是空间利用率的提高终归有限,所以摩尔在1975年修正了他的预测,把晶体管密度的增速,从每年翻番变成每两年翻一番.

以内存芯片为例, 2000 年的 DRAM, 204 平方毫米的面积上有 256,000, 000 个晶体管. 和 1975年相比, 晶体管密度 25年增加了 6300 倍. (如果按照摩尔定律两年翻一番的速度, 25年是增加 5800 倍左右, 基本上比较接近)

相应芯片的存储容量则从 0.001 Mb 增加到 256 Mb, 扩大了二十五万倍.

传统工程设计上, 往往需要权衡多种因素的利弊. 但在相当长一段时间内, 晶体管小型化在实践上不仅增加密度,而且使晶体管速度更快,能耗更低,不需要担心其它因素的限制.

平均每两年换一代的芯片生产技术,栅长缩小30% (x 0.7) ,相应的晶体管密度翻番,晶体管之间的延迟缩短30%, 导致相应的时钟频率增加40%,晶体管的电压减少30%, 单位能耗则减少50%. 由于晶体管整体数目翻番,所以整体能耗不变,但电路整体快了 40%.

但是到了本世纪初,晶体管的小型化遇到了瓶颈, 当栅长低于100纳米以后,晶体管漏电的问题变得严重,成了一个不可忽视的问题.

(未完待续)

0

推荐

京公网安备 11010502034662号

京公网安备 11010502034662号