(1)

晶体管本质, 就是用"开"和"关"的状态,表示二进制里的 1 和 0.

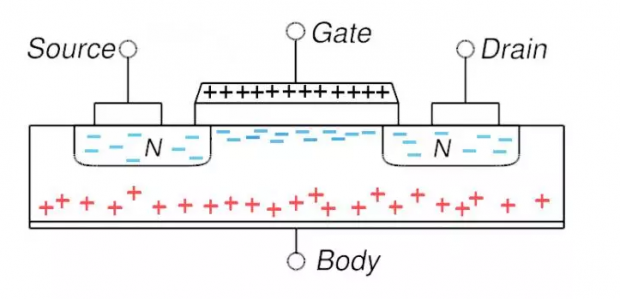

集成电路里的所谓场效应管 (Field-Effect Transistor), 主要是三个部分: 源极 (Source), 栅极 (Gate) ,漏极 (Drain). 栅极本质上是一个电容, 对其施加电压时,栅极下面的沟道 (Channel) 联通源极和漏极,晶体管开启,代表"1"的状态. 电压取消时,电流降为零,晶体管关闭, 代表"0"的状态.

人们通常说的 CPU 的时钟频率, 就是晶体管开关的速度. 1 Ghz 就是 1秒钟内可以开关十亿次.

为什么人类的计算革命,选择了晶体管?

因为晶体管的持续小型化,使得单位生产成本的计算能力, 不断指数型的迅速增长.

与之相比,古老的算盘,算珠拨弄的速度 (类似晶体管开关的速度),和数据的容量,两千多年来没有实质的提高.

(2)

随着晶体管不断小型化,各种漏电问题成为摩尔定律发展的重大障碍.漏电意味着能量消耗的大大增加, 芯片过热甚至失效.

一类比较典型的漏电是所谓的 "栅氧化层泄露" (Gate Oxide Leakage).

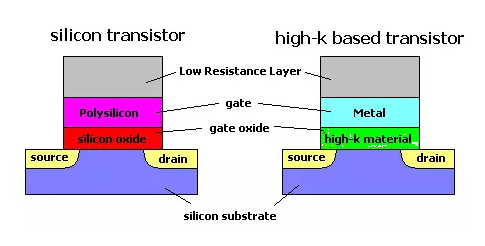

传统的场效应管的栅极 (Gate) 底下是一层二氧化硅 (Silicon Oxide) 的材料, 其厚度随着晶体管小型化也相应减少 (否则会影响栅极的电容和晶体管的性能). 当栅极长度缩减到 45 纳米量级时, 二氧化硅的有效厚度只有一纳米左右, 由于量子隧穿的效应,会导致栅极的严重漏电现象.

最终英特尔经过千万次实验后推出的解决方案, 是使用一种 "高介电常数" (high dielectric) 的材料, 以金属铪(Hafnium) 氧化物为基础的材料,取代二氧化硅, 其物理厚度没有减小, 但不会影响栅极的电容量.

2007年英特尔推出的 45纳米的芯片,栅极漏电比上一代技术减少了90%以上.

(3)

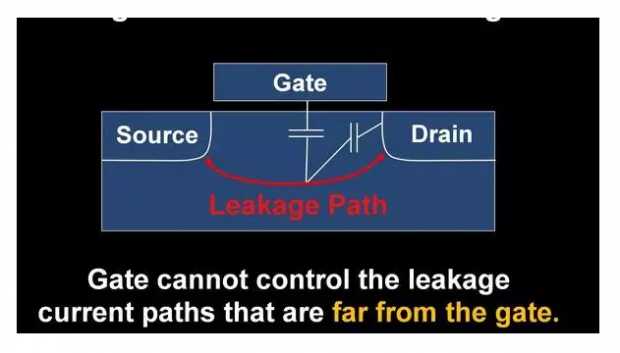

另一类漏电,来自所谓的"短沟道效应" (Short Channel Effect)的问题.简言之,就是晶体管栅极长度不断缩小,晶体管导电的阈值电压不断下降,零电压时的还有微弱的电流经过.

这个问题的本质, 是在栅极很短的时候,漏极本身也成了一个电容,和栅极竞争了.栅极越小,在离栅极较远的地方,源极和漏极之间的漏电无法控制. 如下图.

1996 年, 当工业界还在生产250纳米的芯片时, 大众的观点是晶体管小型化到 100纳米以下几乎不可能. 但是美国国防先进研究项目总署 (DARPA)已经在思考小型化到 25 纳米时,短沟道效应导致的漏电挑战了.

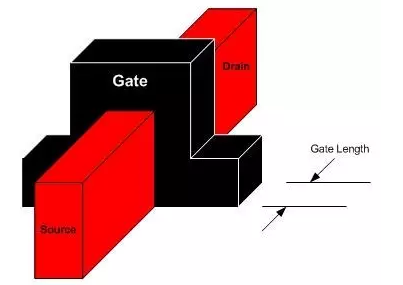

加州大学伯克利分校的胡正明教授, 1997年获得 DARPA 资助, 提出了 FinFET 的设计概念. 其思路本质,是在三个侧面用栅极把晶体管包住,这样源极和漏极的任何通道,离栅极都不会太远,短沟道效应带来的漏电现象大大减弱.

这个设计,因为形状像鱼鳍 (Fin), 所以也被称为 FinFET. (FET 是"场效应管"的英文缩写)

十几年后, 在克服各种生产技术挑战后, 2011年英特尔在 22 纳米芯片中第一次使用了 FinFET 的技术. 这个技术被戈登*摩尔称为是"四十年来半导体行业中最激进的改动".

曾撰文提到的 Nvidia 2016年最新的 GPU? 它采用的是台积电最新的16纳米的FinFET 生产技术.

(4)

如果以史为鉴,突破晶体管小型化的物理极限,并没有观察者现在那么悲观. 原来看似无法逾越的问题,换个不同的角度会有意向不到的解决方案.

摩尔定律最初说的是晶体管的密度.

密度增加, 意味着晶体管小型化, 意味着单位成本的集成电路,在能耗不变的情况下, 其计算能力会不断提高.

小型化只是表象,在生产成本和能耗不变的情况下,提高计算能力,才是摩尔定律的精髓. 按照这个思路, 推动摩尔定律前进的路径实际上还有很多.

(未完待续)

0

推荐

京公网安备 11010502034662号

京公网安备 11010502034662号